中断与事件

中断与事件

Kayer中断系统

1.中断概述

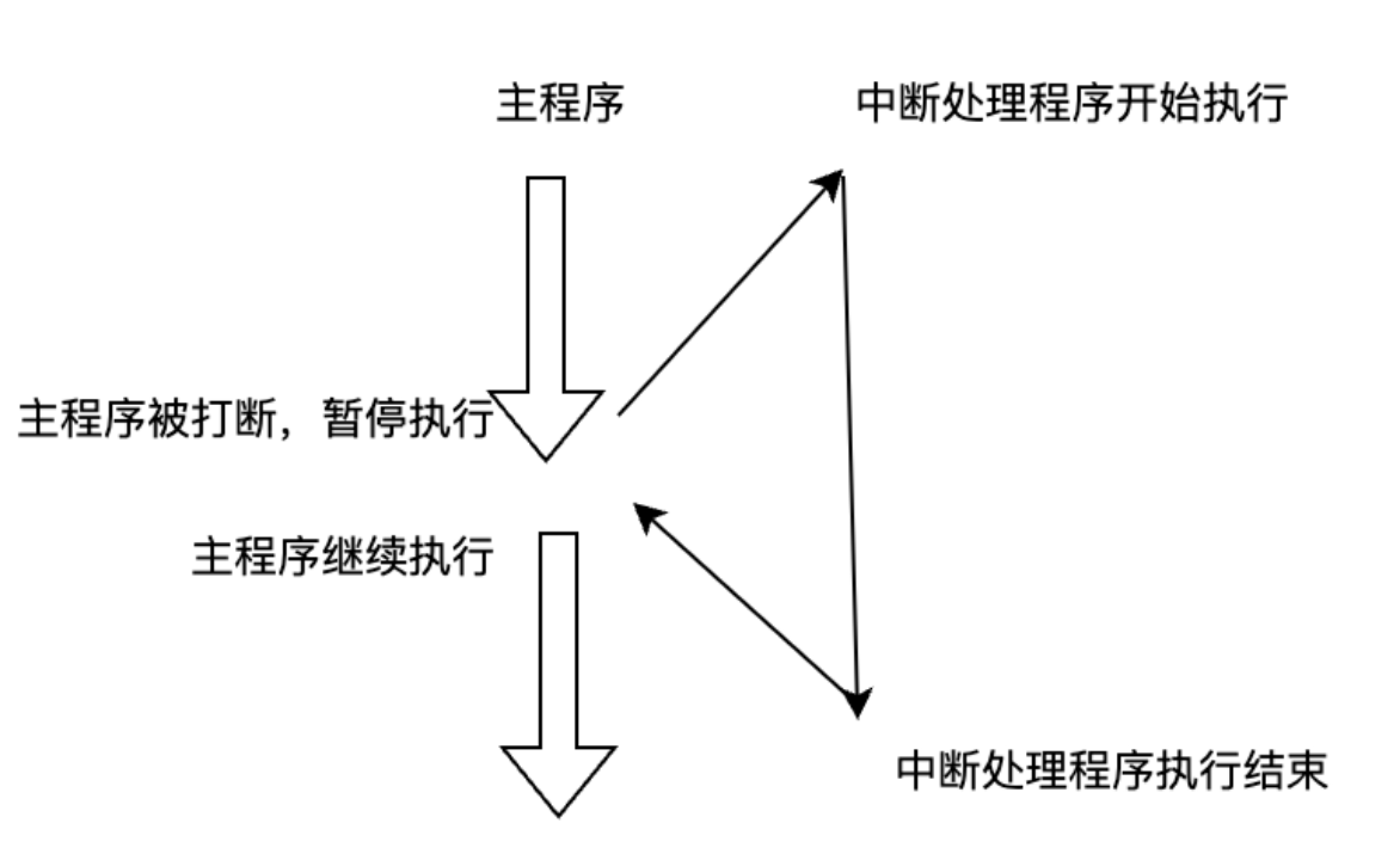

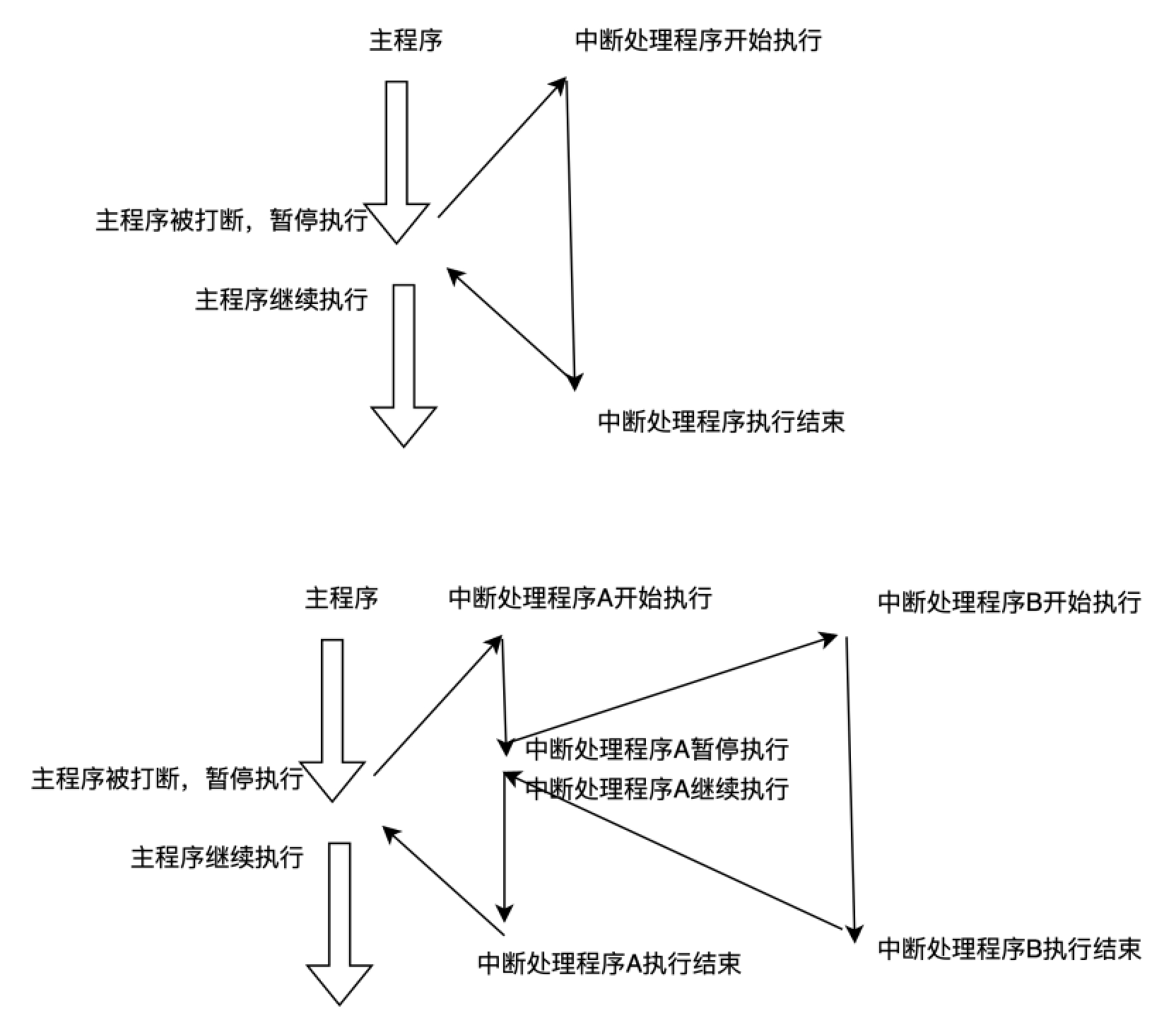

在主程序运行过程中,出现了特定事件,使得CPU暂停当前正在运行的程序,转而去处理这个事件,等这个事件处理完成之后,CPU再回到刚才被打断的位置继续处理,这就是中断。

这个打断CPU执行的特定事件,一般称之为中断源。被中断源打断的位置,称为断点。处理特定事件的过程,称为执行中断处理程序。

当然中断也是可以嵌套的,即中断嵌套。CPU会根据优先级的不同,来决定执行顺序

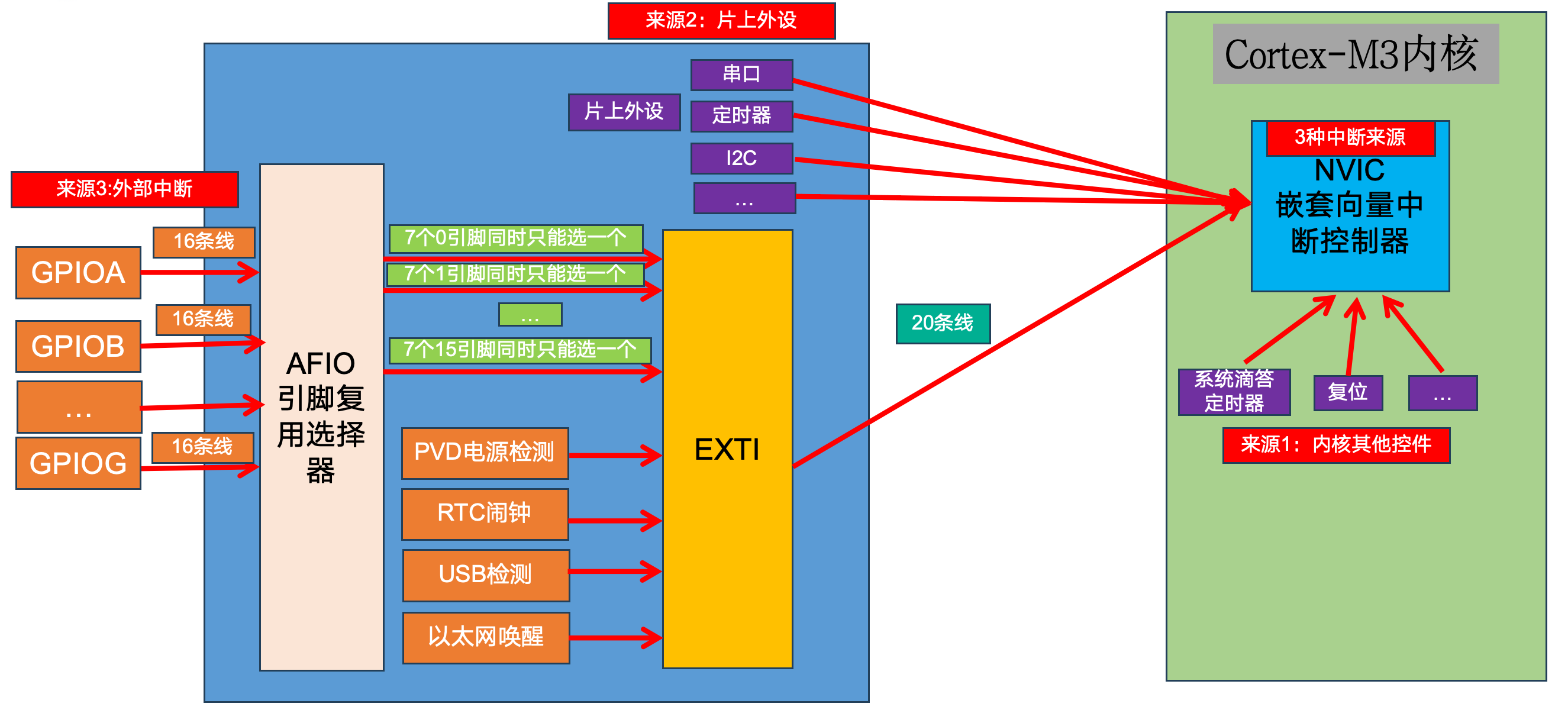

中断源可以是外部的,也可以是内部的。外部的叫外部中断源,内部的叫内部中断源(内部的中断有时候也叫异常)

Cortex-M3内核支持256个中断,其中包含了16个内核中断和240个外部中断,并且具有256级的可编程中断设置。

一般情况下,芯片厂商会对Cortex-M3的中断进行裁剪。具体中断信息可通过对应的芯片手册查看。

2. 中断向量表

STM32的中断向量表是一个储存中断处理函数地址的数组,位于Flash区的起始位置。每个数组元素对应一个中断源,其地址指向相应的中断服务程序。当中断发生时,处理器会根据中断号查找向量表,然后跳转到对应的中断服务程序执行。

中断向量表的主要作用是解决中断函数地址不固定与中断必须跳转到固定地方执行程序之间的矛盾。由于编译器每次编译都会为中断函数随机分配地址,但硬件要求中断必须跳转到固定的位置。因此,中断向量表就作为这样一个固定的地址列表,其中包含了中断函数的地址以及跳转到这些地址的程序。当中断发生时处理器就会跳转到这个固定的中断向量表,然后根据其中的信息跳转到相应的中断处理函数,从而执行中断。

中断向量表可在启动文件中查看(.s文件)

2. NVIC

NVIC(Nested vectored interrupt controller嵌套向量中断控制器)和处理器核的接口紧密相连,可以实现低延迟的中断处理和高效地处理中断。嵌套向量中断控制器管理着包括内核异常,外部中断等所有中断。由NVIC决定哪个中断的处理程序交给CPU来执行。

Cortex-M3内核支持256个中断,其中包含了16个内核中断和240个外部中断,并且具有256级的可编程中断设置。

一般情况下,芯片厂商会对Cortex-M3的中断进行裁剪。

每一个外部中断都可以被使能或者禁止,并且可以被设置为挂起状态或者清除状态。处理器的中断可以是电平形式的,也可以是脉冲形式的,这样中断控制器就可以处理任何中断源。

16个IO的中断与PVD(电源电压检测),RTC(实时时钟),USB,以太网检测这20个外部中断会通过EXTI来控制,然后交给NVIC。其他中断都是直接交给NVIC来处理。

3. 中断优先级

NVIC为了方便管理中断,可以通过软件给每个中断设置优先级。NVIC用4个位来控制优先级,值小的优先级高。把优先级分为两种:抢占优先级和响应优先级。

规则:

- 优先级值越小,优先级越高。

- 如果不设置优先级,则默认优先级为0。

- 先比较抢占优先级。抢占优先级高的可以打断抢占优先级低的。

- 若抢占优先级一样,再比较响应优先级。但是响应优先级不会导致中断嵌套。

- 若抢占优先级一样的同时挂起,则优先处理响应抢占优先级高的。

- 若挂起的优先级(抢占和响应)都一样,则查找中断向量表,值小的先响应。

NVIC对优先级分了5组,在程序中先对中断进行分组,而且分组只能分一次,若多次分,只有最后一次生效。

| 优先级分组 | AIRCR[10:8] | 抢占优先级 | 响应优先级 |

|---|---|---|---|

| 0 | 111 | 0位 取值范围:0 | 4位 取值范围:0-15 |

| 1 | 110 | 1位 取值范围:0-1 | 3位 取值范围:0-7 |

| 2 | 101 | 2位 取值范围:0-3 | 2位 取值范围:0-3 |

| 3 | 100 | 3位 取值范围:0-7 | 1位 取值范围:0-1 |

| 4 | 011 | 4位 取值范围:0-15 | 0位 取值范围:0 |

4. NVIC寄存器

| 寄存器名称 | 位数 | 寄存器个数 | 说明 |

|---|---|---|---|

| 中断使能寄存器(ISER) | 32 | 8 | 每个位控制一个中断 |

| 中断失能寄存器(ICER) | 32 | 8 | 每个位控制一个中断 |

| 应用程序中断及复位控制寄存器(AIRCR) | 32 | 1 | 位[10:8]控制优先级分组 |

| 中断优先级寄存器(IPR) | 8 | 240 | 8个位对应一个中断,而STM32只使用高4位 |

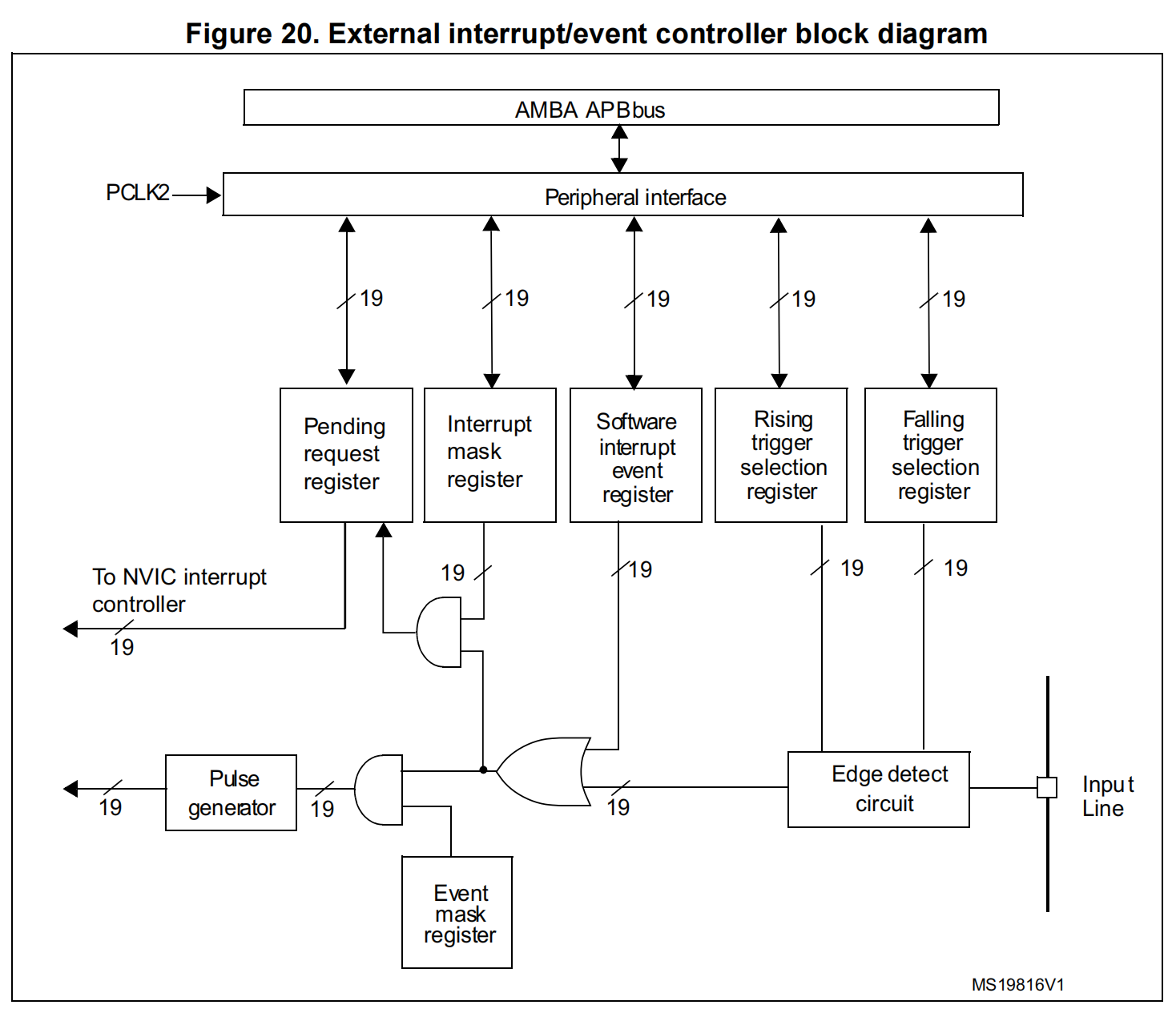

5. EXTI

External interrupt/event controller (EXTI),外部中断/事件控制器由最多20个边缘检测器组成,用于连接线设备,或者在其他设备中由19个边缘检测器用于生成事件/中断请求。每个输入线可以独立配置以选择类型(事件或中断)和相应的触发事件(上升沿或下降沿或两者)。每条线也可以独立屏蔽。一个待处理寄存器维护中断请求的状态线。

EXTI控制器的主要特点如下:

- 每个中断/事件线路上独立的触发和屏蔽

- 每个中断线路都有专用的状态位

- 可生成多达20个软件事件/中断请求

- 能检测脉冲宽度低于APB2时钟周期的外部信号。

EXTI支持的触发方式:上升沿,下降沿,双边沿或软件触发。

EXTI支持所有的GPIO口。

相同的Pin不能同时触发中断。如PA0和PB0不能同时配置为中断源。

EXTI提供了16个GPIO_Pin的中断线,以及额外的中断线如PVD输出,RTC闹钟,USB唤醒和以太网唤醒。

6. 中断/事件

中断会打断当前CPU正在执行的程序,转而去执行中断服务程序,待中断服务程序执行完毕后,CPU会返回到原来的程序执行点继续执行。

事件只是简单地表示某个动作或状态的变化,而不会打断CPU当前正在执行的程序。当事件发生时,它会根据配置来决定是否触发相应的中断。如果开放了对应的中断屏蔽位,事件就可以发生相应的中断,否则事件只会作为一个信号存在,不会被CPU处理。